Chapter 8: Memory Management

Created: 2025-12-16

Updated: 2025-12-16

Multistep Processing of a Program

Address Binding Timing

.BS+0x1234)0xABCD)0x18)0x18)#include <dlfcn.h>

int main() {

double (*cosine)(double);

void* handle = dlopen ("/lib/libm.so.6", RTLD_LAZY);

cosine = dlsym(handle, "cos");

printf ("%f\n", (*cosine)(2.0));

dlclose(handle);

}

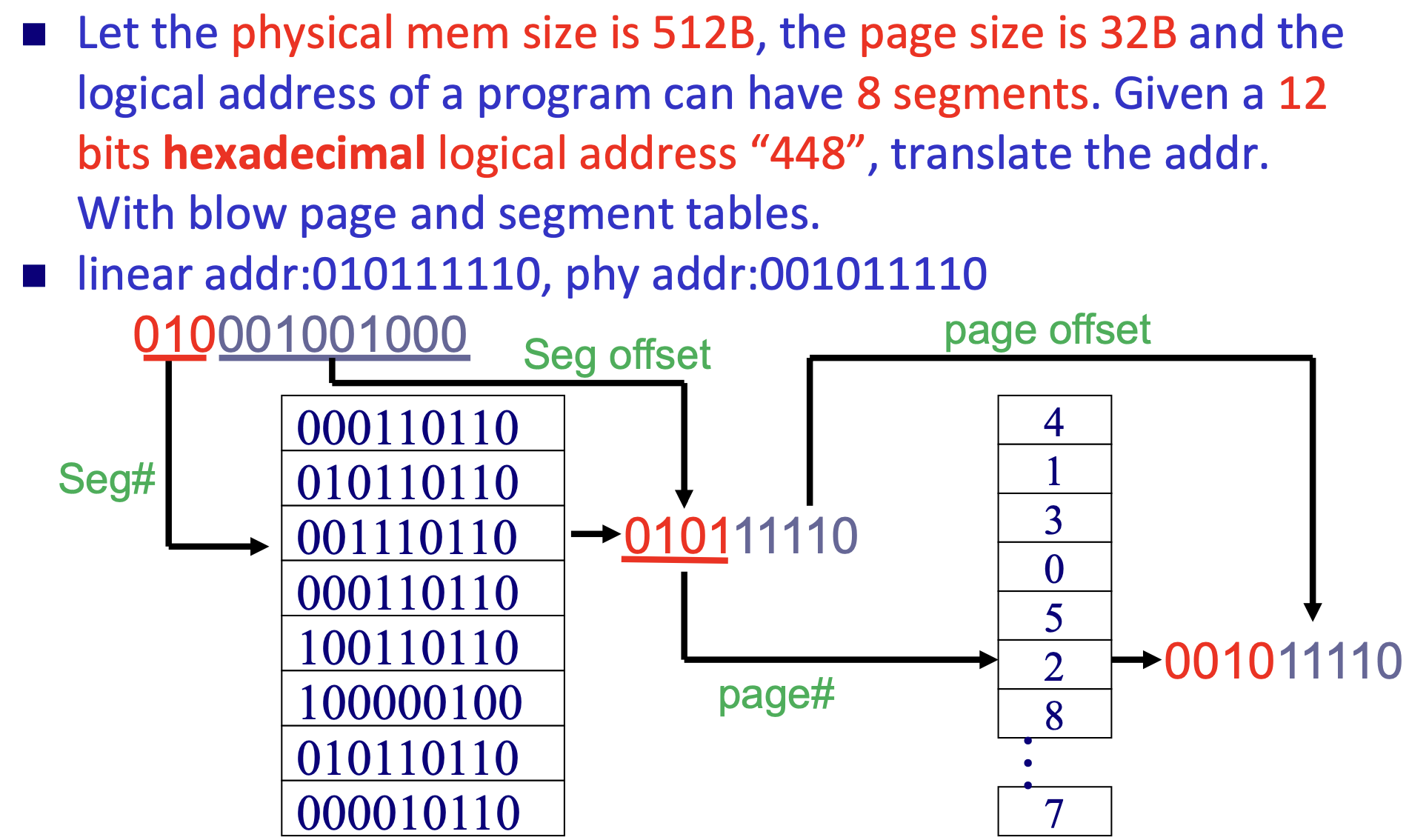

stub call -> check if library is in memory -> if not, load it -> execute the libn pages, need to find n free frames and load the programp: base address of a pagef: base address of a framep) + page offset (d)

N bits of p -> can allocate at most pages -> 16, offset 32)

13, GDT/LDT 1, protection info 2

M bits of d -> bytesf) + page offset (d)p + d; p --MMU-> f; f + d# of pages: determine the logical memory size of a process# of frames: depending on the size of physical memory2 memory accesses -> solved by TLBPage table would be huge and difficult to be loaded. e.g. 4GB () logical memory with 4KB () page would have 1 million () pages table entries. Three solutions:

d -> 4KB () page sizep1) + 10 (p2) + 12 (d)p1 can be used as a page size flag

p2 + 12 d)d)